캐시 메모리는 컴퓨터 시스템의 성능을 향상시키기 위해 사용되는 중요한 요소 중 하나입니다. 주로 프로세서와 주 기억장치(주 메모리) 간의 속도 차이를 극복하기 위한 목적으로 사용됩니다.

캐시 메모리는 주로 빠른 속도로 접근할 수 있는 작은 용량의 메모리입니다. 이를 통해 프로세서가 더 빠르게 데이터에 접근할 수 있어 전반적인 시스템 성능이 향상됩니다.

캐시 메모리의 종류

레벨 1 캐시(L1 Cache): 프로세서에 내장된 가장 빠른 캐시로, 소량의 데이터와 명령어를 저장합니다.

레벨 2 캐시(L2 Cache): L1 캐시보다 크고 느리지만 여전히 빠른 캐시로, 여러 코어가 공유하는 경우가 많습니다.

레벨 3 캐시(L3 Cache): 더 크고 느린 캐시로, 여러 코어 사이에서 공유됩니다. L3 캐시메모리는 코어 외부에 위치합니다.

참조 지역성의 원리

캐시 메모리는 용량이 적기 때문에 CPU가 필요할 데이터를 미리 예측하여 적재하는 경우가 있습니다. 이 때, 캐시 메모리에 CPU가 원하는 데이터가 있는지에 따라 캐시 히트와 캐시 미스로 나뉘게 됩니다.

- 캐시 히트(Cache Hit): 캐시에서 데이터를 찾는 데 성공하는 경우. 캐시에 이미 해당 데이터가 존재함.

- 캐시 미스(Cache Miss): 캐시에서 데이터를 찾지 못하는 경우. 데이터를 주 메모리에서 가져와야 함.

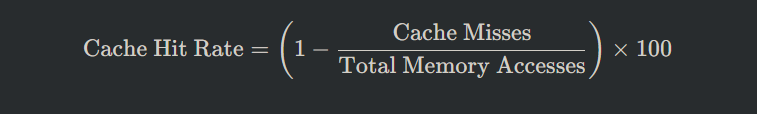

캐시 적중률(Cache Hit Rate)

캐시에서 원하는 데이터를 찾는데 성공한 비율을 나타냄. 공식은 다음과 같음:

높은 캐시 적중률은 효율적인 캐시 사용을 나타내며, 이는 전체 시스템의 성능 향상과 관련이 있습니다. 따라서 프로그래머와 컴파일러는 참조 지역성의 원리를 고려하여 데이터 액세스 패턴을 최적화하고, 이를 통해 캐시 적중률을 높이려고 노력합니다. 참고로 요즘 컴퓨터의 캐시 적중률은 80% 정도 됩니다.

적중률을 올리기 위해 캐시 메모리가 가지는 특징이 있습니다.

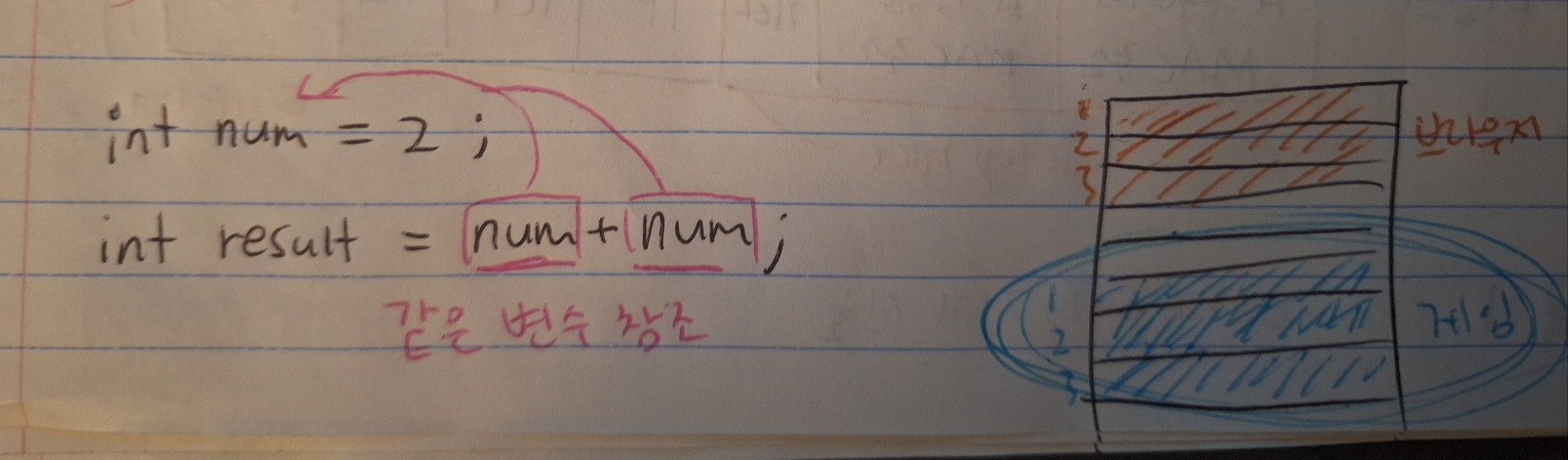

- 시간적 지역성(Temporal Locality): 한 번 참조된 데이터가 잠시 후에 다시 참조될 가능성이 높다. 주로 변수나 루프, 반복문에서 나타남. 예를 들어, CPU는 한 번 선언된 변수에 계속 접근하려는 경향을 가짐

- 공간적 지역성(Spatial Locality): 참조된 데이터 근처의 데이터도 참조될 가능성이 높다. 연속적으로 메모리에 저장된 데이터가 함께 참조되는 경우가 이에 해당함. 예를 들어, 게임 데이터가 모여 있는 공간을 계속 살피게 되는 경향

캐시 라인(Cache Line)

캐시 라인(Cache Line)은 캐시 메모리에서 데이터를 읽거나 쓸 때 사용되는 작은 블록 단위를 나타냅니다. 메모리 시스템은 데이터를 블록 단위로 전송하므로, 캐시 역시 메모리의 데이터를 캐시 라인이라 불리는 고정된 크기의 블록 단위로 저장합니다.

캐시 메모리는 프로세서와 주 메모리 사이의 속도 차이를 줄여 전체 시스템 성능을 향상시키는 역할을 합니다. 특히, 반복적으로 사용되는 데이터에 높은 효과를 발휘하며, 현대 컴퓨터 아키텍처에서는 거의 모든 시스템에서 캐시 메모리를 사용하고 있습니다.

캐시 메모리 (Cache Memory): A high-speed temporary storage space located between the processor and main memory, primarily used to store frequently accessed data and improve overall system performance.

참조 지역성의 원리 (Principle of Locality): The principle that states when data or instructions are accessed once, there is a high probability they will be accessed again shortly afterward, reflecting temporal locality, and that nearby data will also likely be accessed, reflecting spatial locality.

캐시 히트 (Cache Hit): The successful retrieval of data from the cache, indicating that frequently accessed data is already present in the cache.

캐시 적중률 (Cache Hit Rate): A percentage measure representing the ratio of successful cache hits to the total memory accesses, indicating the efficiency of the cache.

캐시 미스 (Cache Miss): The situation where data is not found in the cache, necessitating the retrieval of the required data from the main memory.

시간의 지역성 (Temporal Locality): The aspect of the principle of locality stating that if data is accessed once, there is a high likelihood it will be accessed again shortly afterward.

공간의 지역성 (Spatial Locality): The aspect of the principle of locality stating that data accessed is likely to be in proximity to other accessed data.

'Computer Science > Computer Structure' 카테고리의 다른 글

| 14 RAID (1) | 2024.01.05 |

|---|---|

| 13 Hard disk & Flash memory (보조기억장치) (1) | 2024.01.05 |

| 11 RAM (1) | 2023.12.30 |

| 10 명령어 집합 구조 (Feat. CISC & RISC) (0) | 2023.12.29 |

| 9 명령어 병렬 처리 기법 (1) | 2023.12.28 |

댓글